|

Data Structures | |

| struct | IfxEth_AltRxDescr0_Bits |

| Structure for Alternate/Enhanced RX descriptor DWORD 0 Bit field access. More... | |

| struct | IfxEth_AltRxDescr1_Bits |

| Structure for Alternate/Enhanced RX descriptor DWORD 1 Bit field access. More... | |

| struct | IfxEth_AltTxDescr0_Bits |

| Structure for Alternate/Enhanced TX descriptor DWORD 0 Bit field access. More... | |

| struct | IfxEth_AltTxDescr1_Bits |

| Structure for Alternate/Enhanced TX descriptor DWORD 1 Bit field access. More... | |

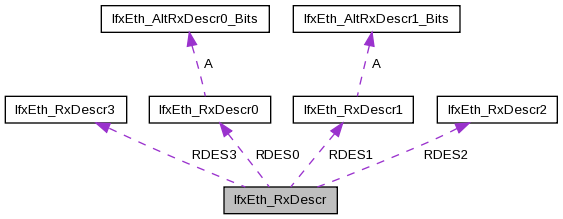

| struct | IfxEth_RxDescr |

| Normal RX descriptor. More... | |

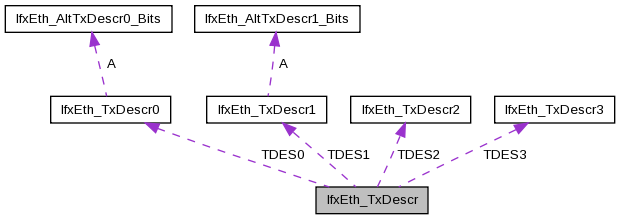

| struct | IfxEth_TxDescr |

| Normal TX descriptor. More... | |

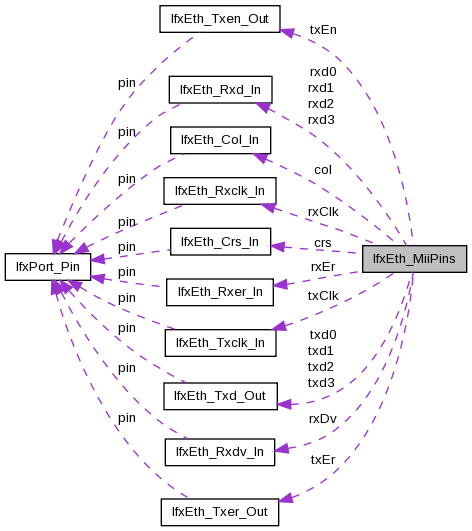

| struct | IfxEth_MiiPins |

| Port pins for MII mode configuration. More... | |

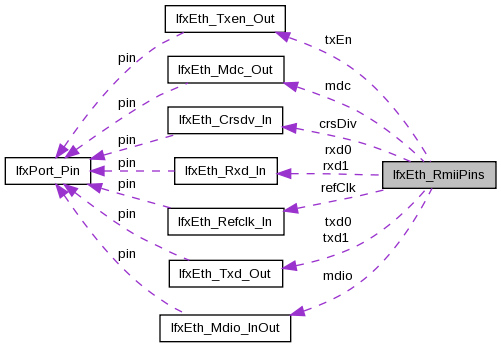

| struct | IfxEth_RmiiPins |

| Port pins for RMII mode configuration. More... | |

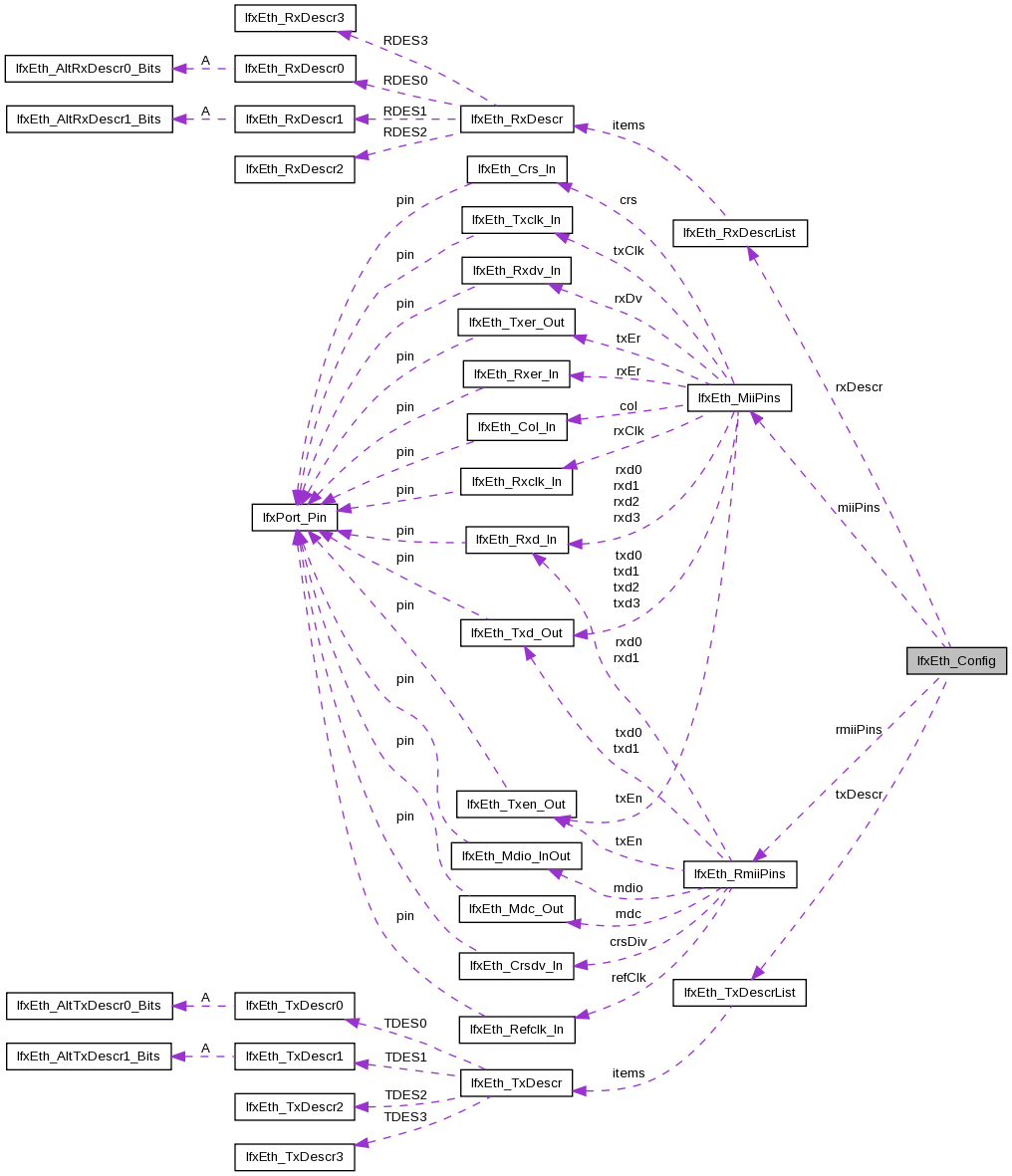

| struct | IfxEth_Config |

| ETH configuration structure. More... | |

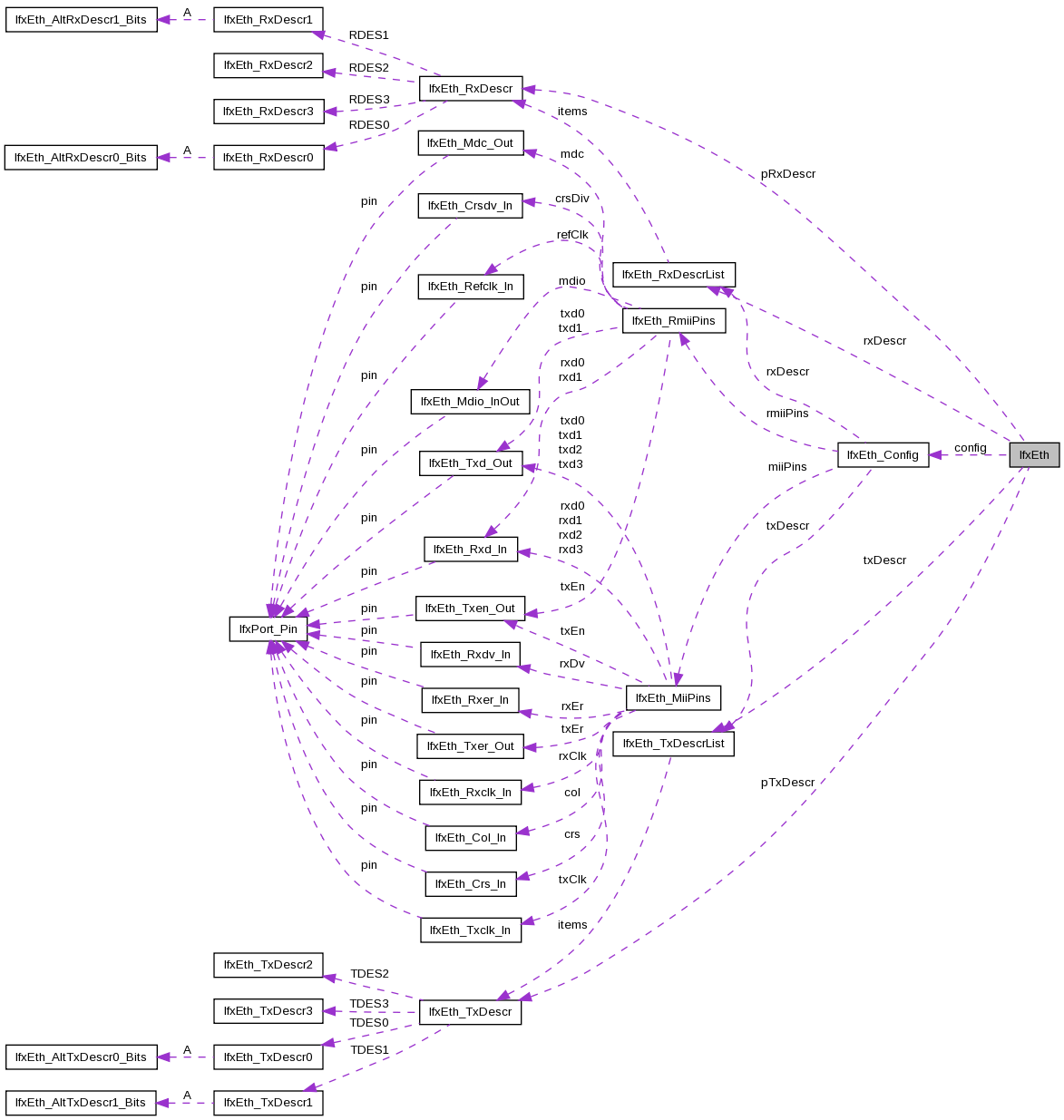

| struct | IfxEth |

| ETH driver structure. More... | |

| struct | IfxEth_RxDescr0_Bits |

| Structure for RX descriptor DWORD 0 Bit field access. More... | |

| struct | IfxEth_RxDescr1_Bits |

| Structure for RX descriptor DWORD 1 Bit field access. More... | |

| struct | IfxEth_TxDescr0_Bits |

| Structure for TX descriptor DWORD 0 Bit field access. More... | |

| struct | IfxEth_TxDescr1_Bits |

| Structure for TX descriptor DWORD 1 Bit field access. More... | |

Detailed Description

Data Structure Documentation

| struct IfxEth_AltRxDescr0_Bits |

Structure for Alternate/Enhanced RX descriptor DWORD 0 Bit field access.

| Data Fields | ||

|---|---|---|

| uint32 | AFM: 1 | Destination Address Filter Fail. |

| uint32 | CE: 1 | CRC Error. |

| uint32 | DBE: 1 | Dribble Bit Error. |

| uint32 | DE: 1 | Descriptor Error. |

| uint32 | ES: 1 | Error Summary, ES = PCE | CE | RE | RWT | LC | IPC | OE | DE. |

| uint32 | ext: 1 | Extended Status Available/Rx MAC Address. |

| uint32 | FL: 14 | Frame Length. |

| uint32 | FS: 1 | First Descriptor. |

| uint32 | FT: 1 | Frame Type. |

| uint32 | IPC: 1 | IPC Checksum Error/Giant Frame. |

| uint32 | LC: 1 | Late Collision. |

| uint32 | LE: 1 | Length Error. |

| uint32 | LS: 1 | Last Descriptor. |

| uint32 | OE: 1 | Overflow Error. |

| uint32 | OWN: 1 | Own Bit, 1 = own by DMA. |

| uint32 | RE: 1 | Receive Error. |

| uint32 | RWT: 1 | Receive Watchdog Timeout. |

| uint32 | SAF: 1 | Source Address Filter Fail. |

| uint32 | VLAN: 1 | VLAN Tag. |

| struct IfxEth_AltRxDescr1_Bits |

Structure for Alternate/Enhanced RX descriptor DWORD 1 Bit field access.

| Data Fields | ||

|---|---|---|

| uint32 | DIC: 1 | Disable Interrupt on Completion. |

| uint32 | RBS1: 13 | Receive Buffer 1 Size. |

| uint32 | RBS2: 13 | Receive Buffer 2 Size. |

| uint32 | RCH: 1 | Second Address Chained. |

| uint32 | RER: 1 | Receive End of Ring. |

| uint32 | resv: 2 | reserved) |

| uint32 | resv1: 1 | reserved |

| struct IfxEth_AltTxDescr0_Bits |

Structure for Alternate/Enhanced TX descriptor DWORD 0 Bit field access.

| Data Fields | ||

|---|---|---|

| uint32 | CC: 4 | Collision count. |

| uint32 | CIC: 2 | Checksum Insertion Control. |

| uint32 | DB: 1 | Deferred bit. |

| uint32 | DC: 1 | Disable CRC. |

| uint32 | DP: 1 | Disable Padding. |

| uint32 | EC: 1 | Excessive Collision. |

| uint32 | ED: 1 | Excessive deferral. |

| uint32 | ES: 1 | Error Summary, ES = JT | FF | LOC | NC | LC | EC | ED | UF. |

| uint32 | FF: 1 | Frame Flushed. |

| uint32 | FS: 1 | First Segment. |

| uint32 | IC: 1 | Interrupt on Completion. |

| uint32 | IHE: 1 | IP Header Error. |

| uint32 | JT: 1 | Jabber Timeout. |

| uint32 | LC: 1 | Late Collision. |

| uint32 | LOC: 1 | Loss of Carrier. |

| uint32 | LS: 1 | Last Segment. |

| uint32 | NC: 1 | No Carrier. |

| uint32 | OWN: 1 | Own Bit, 1 = own by DMA. |

| uint32 | PCE: 1 | Payload Checksum Error. |

| uint32 | resv: 2 | (reserved) |

| uint32 | resv1: 1 | (Reserved) |

| uint32 | TCH: 1 | Second Address Chained. |

| uint32 | TER: 1 | Transmit End of Ring. |

| uint32 | TTSE: 1 | Transmit Time Stamp Enable. |

| uint32 | TTSS: 1 | Transmit Time Stamp Status. |

| uint32 | UF: 1 | Underflow error. |

| uint32 | VLAN: 1 | VLAN TAG. |

| struct IfxEth_AltTxDescr1_Bits |

| struct IfxEth_RxDescr |

| Data Fields | ||

|---|---|---|

| IfxEth_RxDescr0 | RDES0 | RX descriptor DWORD 0. |

| IfxEth_RxDescr1 | RDES1 | RX descriptor DWORD 1. |

| IfxEth_RxDescr2 | RDES2 | RX descriptor DWORD 2. |

| IfxEth_RxDescr3 | RDES3 | RX descriptor DWORD 3. |

| struct IfxEth_TxDescr |

| Data Fields | ||

|---|---|---|

| IfxEth_TxDescr0 | TDES0 | TX descriptor DWORD 0. |

| IfxEth_TxDescr1 | TDES1 | TX descriptor DWORD 1. |

| IfxEth_TxDescr2 | TDES2 | TX descriptor DWORD 2. |

| IfxEth_TxDescr3 | TDES3 | TX descriptor DWORD 3. |

| struct IfxEth_MiiPins |

| Data Fields | ||

|---|---|---|

| IfxEth_Col_In * | col | pointer to COL input pin config |

| IfxEth_Crs_In * | crs | pointer to CRS input pin config |

| IfxEth_Rxclk_In * | rxClk | Pointer to RXCLK input pin config. |

| IfxEth_Rxd_In * | rxd0 | Pointer to RXD0 input pin config. |

| IfxEth_Rxd_In * | rxd1 | Pointer to RXD1 input pin config. |

| IfxEth_Rxd_In * | rxd2 | Pointer to RXD2 input pin config. |

| IfxEth_Rxd_In * | rxd3 | Pointer to RXD3 input pin config. |

| IfxEth_Rxdv_In * | rxDv | Pointer to RXDV input pin config. |

| IfxEth_Rxer_In * | rxEr | Pointer to RXER input pin config. |

| IfxEth_Txclk_In * | txClk | Pointer to TXCLK input pin config. |

| IfxEth_Txd_Out * | txd0 | Pointer to TXD0 output pin config. |

| IfxEth_Txd_Out * | txd1 | Pointer to TXD1 output pin config. |

| IfxEth_Txd_Out * | txd2 | Pointer to TXD2 output pin config. |

| IfxEth_Txd_Out * | txd3 | Pointer to TXD3 output pin config. |

| IfxEth_Txen_Out * | txEn | Pointer to TXEN output pin config. |

| IfxEth_Txer_Out * | txEr | Pointer to TXER output pin config. |

| struct IfxEth_RmiiPins |

| Data Fields | ||

|---|---|---|

| IfxEth_Crsdv_In * | crsDiv | pointer to CRSDIV input pin config |

| IfxEth_Mdc_Out * | mdc | Pointer to MDC output pin config. |

| IfxEth_Mdio_InOut * | mdio | Pointer to MDIO pin config. |

| IfxEth_Refclk_In * | refClk | Pointer to REFCLK input pin config. |

| IfxEth_Rxd_In * | rxd0 | Pointer to RXD0 input pin config. |

| IfxEth_Rxd_In * | rxd1 | Pointer to RXD1 input pin config. |

| IfxEth_Txd_Out * | txd0 | Pointer to TXD0 output pin config. |

| IfxEth_Txd_Out * | txd1 | Pointer to TXD1 output pin config. |

| IfxEth_Txen_Out * | txEn | Pointer to TXEN output pin config. |

| struct IfxEth_Config |

Data Fields | |

| uint8 | macAddress [6] |

| MAC address for the ethernet, should be unique in the network. More... | |

| uint32(* | phyInit )(void) |

| Pointer to the transceiver init function. More... | |

| boolean(* | phyLink )(void) |

| Pointer to the transceiver link function. More... | |

| IfxEth_PhyInterfaceMode | phyInterfaceMode |

| Phy Interface mode. More... | |

| const IfxEth_RmiiPins * | rmiiPins |

| Pointer to port pins configuration of RMII mode. More... | |

| const IfxEth_MiiPins * | miiPins |

| Pointer to port pins configuration of MII mode. More... | |

| Ifx_Priority | isrPriority |

| Interrupt service priority. More... | |

| IfxSrc_Tos | isrProvider |

| Interrupt service provider. More... | |

| Ifx_ETH * | ethSfr |

| Pointer to register base. More... | |

| IfxEth_RxDescrList * | rxDescr |

| pointer to RX descriptor RAM More... | |

| IfxEth_TxDescrList * | txDescr |

| pointer to TX descriptor RAM More... | |

Field Documentation

| Ifx_ETH* ethSfr |

Pointer to register base.

Definition at line 389 of file IfxEth.h.

Referenced by IfxEth_init(), and IfxEth_initConfig().

| Ifx_Priority isrPriority |

| IfxSrc_Tos isrProvider |

| uint8 macAddress[6] |

MAC address for the ethernet, should be unique in the network.

Definition at line 381 of file IfxEth.h.

Referenced by IfxEth_getMacAddressPointer(), and IfxEth_init().

| const IfxEth_MiiPins* miiPins |

Pointer to port pins configuration of MII mode.

Definition at line 386 of file IfxEth.h.

Referenced by IfxEth_init().

| uint32(* phyInit)(void) |

Pointer to the transceiver init function.

Definition at line 382 of file IfxEth.h.

Referenced by IfxEth_init().

| IfxEth_PhyInterfaceMode phyInterfaceMode |

| boolean(* phyLink)(void) |

Pointer to the transceiver link function.

Definition at line 383 of file IfxEth.h.

Referenced by IfxEth_isLinkActive().

| const IfxEth_RmiiPins* rmiiPins |

Pointer to port pins configuration of RMII mode.

Definition at line 385 of file IfxEth.h.

Referenced by IfxEth_init().

| IfxEth_RxDescrList* rxDescr |

| IfxEth_TxDescrList* txDescr |

| struct IfxEth |

| Data Fields | ||

|---|---|---|

| IfxEth_Config | config | Copy of the configuration passed through IfxEth_init() |

| uint32 | error | Indicate an error has occurred during execution. |

| Ifx_ETH * | ethSfr | Pointer to register base. |

| sint32 | isrCount | count of all ISR |

| sint32 | isrRxCount | Count of RX ISR. |

| sint32 | isrTxCount | Count of TX ISR. |

| IfxEth_RxDescr * | pRxDescr | |

| IfxEth_TxDescr * | pTxDescr | |

| uint32 | rxCount | Number of frames received. |

| IfxEth_RxDescrList * | rxDescr | pointer to RX descriptor RAM |

| sint32 | rxDiff | Difference between isrRxCount and rxCount. |

| Ifx_ETH_STATUS | status | Intermediate variable to use register content in control structure. |

| uint32 | txCount | Number of frames transmitted. |

| IfxEth_TxDescrList * | txDescr | pointer to TX descriptor RAM |

| sint32 | txDiff | Difference between isrTxCount and txCount. |

| struct IfxEth_RxDescr0_Bits |

| Data Fields | ||

|---|---|---|

| uint32 | AFM: 1 | Destination Address Filter Fail. |

| uint32 | CE: 1 | CRC Error. |

| uint32 | DBE: 1 | Dribble Bit Error. |

| uint32 | DE: 1 | Descriptor Error. |

| uint32 | ES: 1 | Error Summary, ES = PCE | CE | RE | RWT | LC | IPC | OE | DE. |

| uint32 | FL: 14 | Frame Length. |

| uint32 | FS: 1 | First Descriptor. |

| uint32 | FT: 1 | Frame Type. |

| uint32 | IPC: 1 | IPC Checksum Error/Giant Frame. |

| uint32 | LC: 1 | Late Collision. |

| uint32 | LE: 1 | Length Error. |

| uint32 | LS: 1 | Last Descriptor. |

| uint32 | OE: 1 | Overflow Error. |

| uint32 | OWN: 1 | Own Bit, 1 = own by DMA. |

| uint32 | PCE: 1 | Rx MAC Address/Payload Checksum Error. |

| uint32 | RE: 1 | Receive Error. |

| uint32 | RWT: 1 | Receive Watchdog Timeout. |

| uint32 | SAF: 1 | Source Address Filter Fail. |

| uint32 | VLAN: 1 | VLAN Tag. |

| struct IfxEth_RxDescr1_Bits |

| struct IfxEth_TxDescr0_Bits |

| Data Fields | ||

|---|---|---|

| uint32 | CC: 4 | Collision Count. |

| uint32 | DB: 1 | Deferred Bit. |

| uint32 | EC: 1 | Excessive Collision. |

| uint32 | ED: 1 | Excessive Deferral. |

| uint32 | ES: 1 | Error Summary, ES = JT | FF | LOC | NC | LC | EC | ED | UF. |

| uint32 | FF: 1 | Frame Flushed. |

| uint32 | IHE: 1 | IP Header Error. |

| uint32 | JT: 1 | Jabber Timeout. |

| uint32 | LC: 1 | Late Collision. |

| uint32 | LOC: 1 | Loss of Carrier. |

| uint32 | NC: 1 | No Carrier. |

| uint32 | OWN: 1 | Own Bit, 1 = own by DMA. |

| uint32 | PCE: 1 | Payload Checksum Error. |

| uint32 | resv: 13 | (reserved) |

| uint32 | TTSS: 1 | Tx Time Stamp Status. |

| uint32 | UF: 1 | Underflow Error. |

| uint32 | VLAN: 1 | VLAN Tag. |

| struct IfxEth_TxDescr1_Bits |

| Data Fields | ||

|---|---|---|

| uint32 | CIC: 2 | Checksum Insertion Control. |

| uint32 | DC: 1 | Disable CRC. |

| uint32 | DP: 1 | Disable Padding. |

| uint32 | FS: 1 | First Segment. |

| uint32 | IC: 1 | Interrupt on Completion. |

| uint32 | LS: 1 | Last Segment. |

| uint32 | TBS1: 11 | Transmit Buffer 1 Size. |

| uint32 | TBS2: 11 | Transmit Buffer 2 Size. |

| uint32 | TCH: 1 | Second Address Chained. |

| uint32 | TER: 1 | Transmit End of Ring. |

| uint32 | TTSE: 1 | Transmit Time Stamp Enable. |